Ambarella安霸 何小林

近年来,人工智能应用正经历一轮快速的发展与普及,而以ChatGPT等先进的大模型技术在此过程中起到了关键作用。这些模型对计算能力的需求不断攀升,催生了AI芯片设计的不断革新,进入了大算力时代。

目前,主流AI芯片的架构仍然沿用了传统的冯·诺依曼模型,这一设计将计算单元与数据存储分离。在这种架构下,处理器需要从内存中读取数据,执行计算任务,然后将结果写回内存。尽管AI芯片的算力在不断提升,但仅仅拥有强大的数据计算能力并不足够。当数据传输速度无法跟上计算速度时,数据传输时间将远超过计算时间。

以Transformer架构为基础的AI大模型导致了模型参数量激增,短短两年间模型大小扩大了惊人的410倍,运算量更是激增了高达750倍。尽管硬件的峰值计算能力在过去20年中提升了惊人的60,000倍,但DRAM带宽的增长却相对滞后,仅提高了100倍。计算能力与带宽能力之间的巨大差距导致了内存容量和数据传输速度难以跟上AI硬件的计算速度,这已成为限制AI芯片性能发挥的主要瓶颈,通常被称为“内存墙”问题。

内存墙的应对方法

针对内存墙问题,研究人员正积极探索多种解决方案,主要可分为以下三个研究方向:

1. 算法优化:重新审视网络模型设计,致力于优化算法实现,以减少对高速数据传输的依赖。这一方向旨在从根本上降低数据传输需求,提升算法效率,从而打破内存墙的限制。

2. 模型压缩:通过降低模型精度(如量化)或去除冗余参数(如剪枝)来压缩推理模型。这种方法可以显著减少模型大小,降低内存占用,从而减轻内存墙带来的压力。

3. AI芯片架构设计:设计高效的AI芯片架构,以优化数据流和计算流程。通过硬件层面的创新,减少数据搬运和计算量,提高整体系统效率。

算法的优化与模型的压缩是软件研究人员追求的重要方向。在AI芯片架构设计领域,各大AI芯片公司也开始优化芯片架构, 以实现更为高效的内存传输。安霸同样提出了其专有的解决方案。

CV3系列芯片如何打破内存墙

2015年,安霸收购了自动驾驶算法公司VisLab, 开始研究自动驾驶需要怎样的芯片。 2017年,安霸推出第一代CVflow架构芯片CV1,用于加速AI视觉计算。2018年开始逐步推出并量产专门针对车载辅助驾驶市场的第二代CVflow架构芯片CV2系列。 2019年,自动驾驶技术的突飞猛进,使得汽车行业对芯片算力的需求急剧增长,标志着大算力时代的来临。在这样的技术背景下,安霸前瞻性地启动了CV3系列大算力芯片的设计工作,旨在为自动驾驶场景提供强大的计算能力。经过三年的精心打磨与架构设计, 2022年,CV3架构的第一颗芯片CV3-HD成功点亮, 其最高算力达到了1500 eTOPS(等效算力),而功耗仅为50瓦,展示出了卓越的计算性能与能耗比。 2023年,首个面向量产智驾域控制器的芯片CV3-AD685顺利点亮并开始提供样片,其算力达到750 eTOPS(等效算力)。2024年1月,安霸再次推出了CV3-AD 汽车智驾域控制器芯片的最新成员:CV3-AD635 和 CV3-AD655。至此,CV3-AD 系列芯片已经实现了从主流到中、高端乘用车市场高级辅助驾驶与自动驾驶解决方案的完整覆盖。

在深入洞察自动驾驶场景的基础上,安霸的CV3系列芯片在设计之初就敏锐地预见到大算力时代所带来内存带宽挑战。为了突破内存瓶颈,CV3在内存控制器上采用了先进的LPDDR5技术,每位DRAM的数据传输速率高达8Gb/s。针对不同应用场景的算力需求,设计了64位、128位和256位的内存位宽,从而确保在各种计算场景下都能提供足够的数据传输带宽。

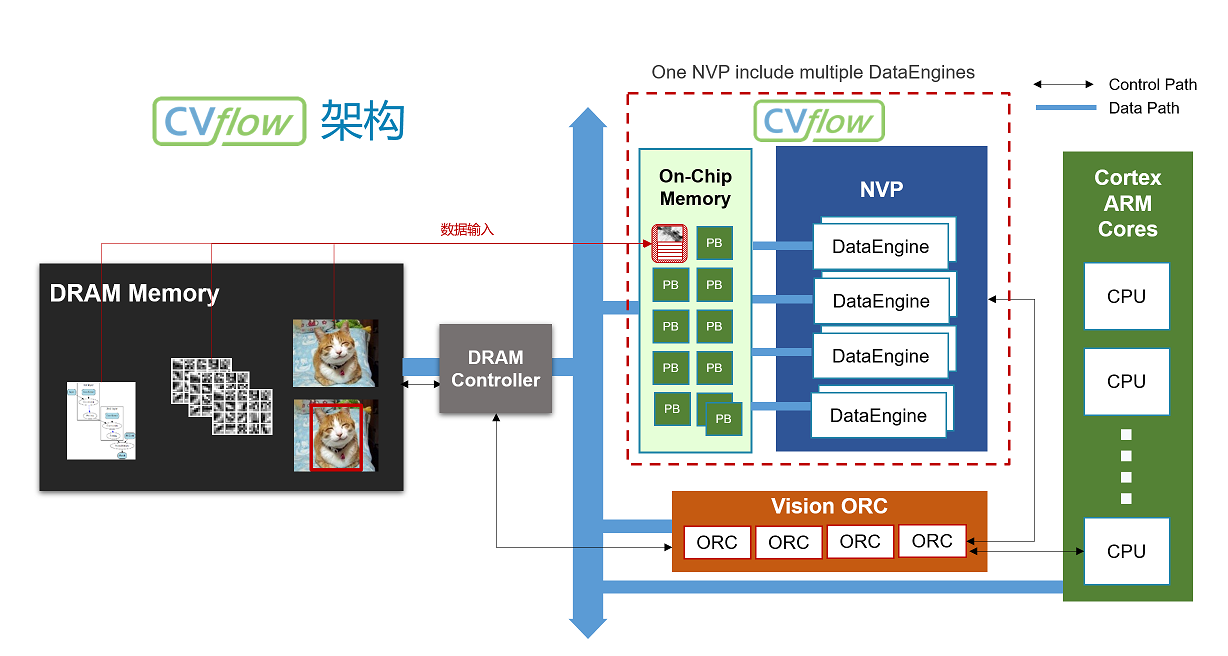

在AI加速器的架构设计上,CV3系列芯片推出了安霸特有的第三代CVflow架构。这一架构赋予了CV3卓越的算力性能和优异的能效比。如图1所示,CVflow的总体架构展示了其数据流和计算单元的组织结构。

图1 CVflow架构图

具体来说, CV3的高算力与低功耗得益于以下几个精心设计的架构特点。

· Partial buffer架构

尽管许多AI芯片采用增大缓存的方式来减少DRAM访问,但缓存系统存在几个显著问题:

1. 设计复杂性与成本:缓存系统的设计相对复杂,相较于同等容量的SRAM,它需要占据更大的芯片面积。这不仅增加了芯片的成本,还可能导致功耗上升。

2. 软件优化需求:为了充分利用缓存系统,软件算法需要针对其进行专门的优化,以提高缓存命中率。这增加了软件开发的复杂性和工作量。

3. 算力浪费:缓存系统通常遵循“使用时才加载”的策略,这导致计算单元在等待数据加载完成期间无法进行有效计算,从而造成算力的浪费。算力的有效利用率在很大程度上依赖于缓存命中率。

4. 性能不稳定:在复杂的多核多线程环境中,缓存命中率与系统的负载密切相关。随着负载的变化,缓存命中率可能会受到严重影响,导致系统性能的不稳定。

与传统的缓存系统不同,CVflow架构采取了一种创新的策略,将片上内存(On-chip Memory)分割成多个不同大小的内存块,这些内存块被称为Partial Buffers(PB)。这些PB的主要用途是存储计算过程中的中间结果,从而显著减少对外部DRAM的访问次数。Partial Buffers所带来的优势如下:

· 简化的硬件设计与成本优化:PB的设计相较于传统缓存更为简单,这意味着在硬件实现上,CVflow架构能够节省更多的芯片面积,进而降低制造成本和功耗。

· 独立的DMA通道:为了确保数据的高效传输,CVflow架构为Partial Buffers配置了独立的DMA(Direct Memory Access)通道。这使得数据能够从DRAM中快速、无缝地传输到PB中,从而避免了数据传输的瓶颈。

· 访存效率高:一次性从DRAM和PB之间传输大块数据的策略, 替代了传统的多次小块数据传输的方式,减少了数据在内存和向量处理器(NVP)之间的搬运数次,降低了数据传输的延迟和开销

· 与计算单元并行处理:PB在CVflow内部被组织成一个环形结构。这意味着当一个PB的数据被使用后,CVflow的硬件调度器会智能地加载下一个所需的数据块到空闲的PB中。这种设计允许数据预加载与计算单元的工作并行进行,从而消除了数据等待时间,提高了整体计算效率。

· 简化的内存管理:与需要手动优化和管理的传统缓存系统不同,CVflow转换工具能够自动、高效地管理PB。这意味着开发人员无需花费额外的时间和精力来管理片上内存,从而可以更加专注于算法和应用的开发。

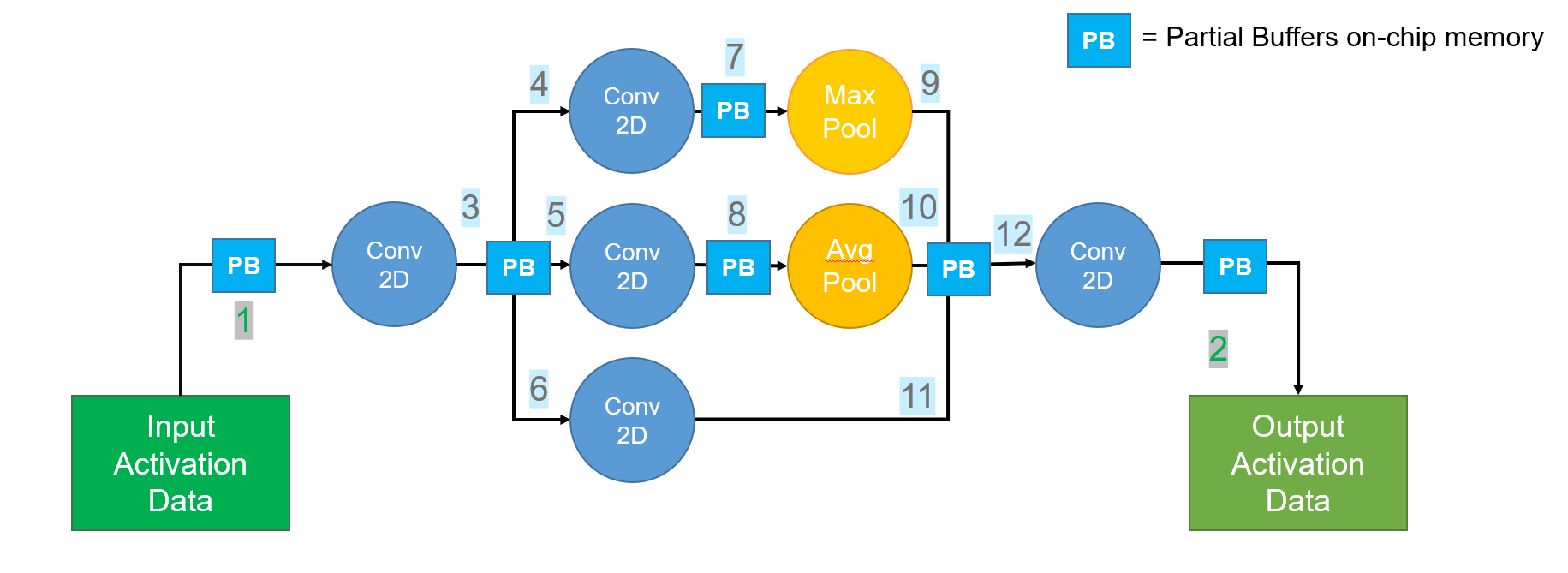

以图2所示的卷积神经网络为例,在传统的计算架构中,该网络通常需要12次的DRAM访问来完成一次完整的计算过程。然而,在CVflow架构下,通过利用高效的Partial Buffers(PB)设计,3到12过程的内存访问被低延迟的PB所取代。这意味着,中间计算结果可以直接在PB中完成,而无需频繁地访问外部的DRAM。因此,整个计算过程中,只需要在输入和输出阶段各进行一次DRAM访问,从而减少了10次的DRAM访问。这种优化不仅显著降低了计算过程中的延迟,还因为减少了外部DRAM的访问次数,从而降低了整体的功耗。

图2 CVflow卷积神经网络计算示例

· 并行的流式架构

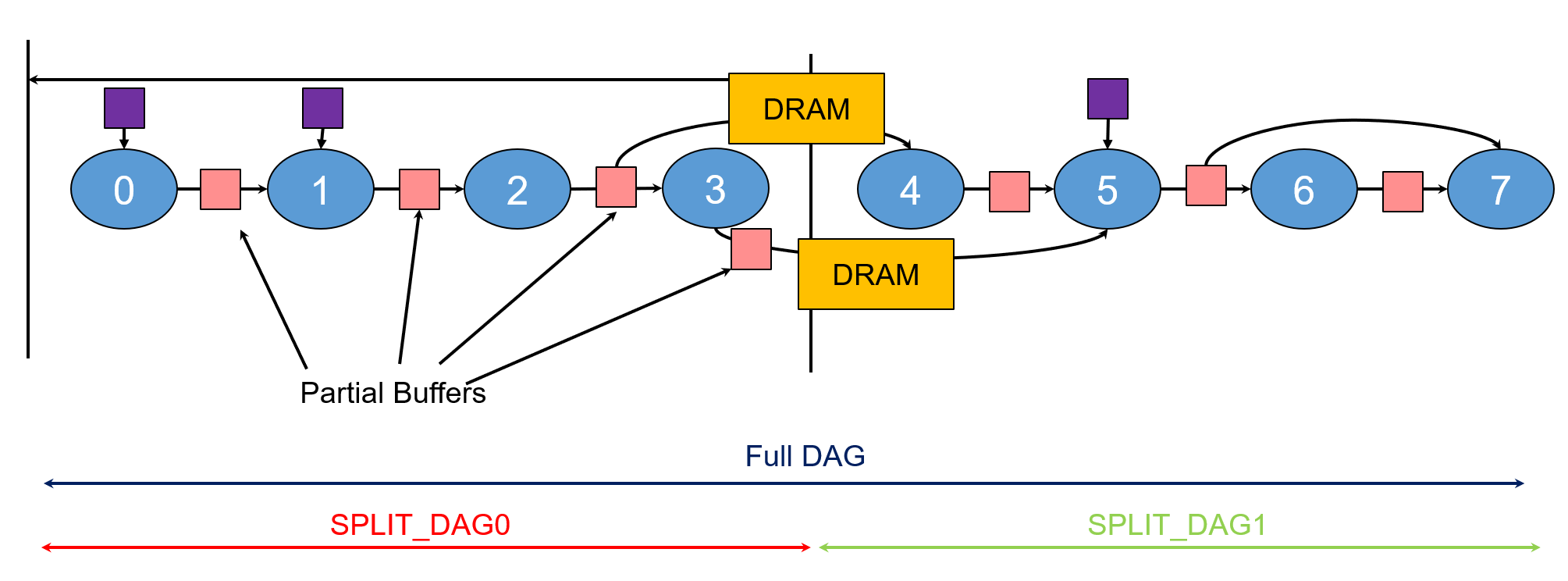

CVflow工具根据芯片的片上内存大小,智能地将大型神经网络切割成多个连续的、紧凑的计算单元,这些单元被组织成有向无环图(DAG)的形式。这种独特的架构带来了多重优势:

· 高效内存利用:每个DAG的中间计算步骤都在片上内存内完成,从而避免了频繁访问外部DRAM的需求。这不仅减少了数据传输的延迟,还提高了内存的使用效率。

· 快速启动与并行处理:网络加载时间大大缩短,因为只需加载一部分网络即可开始计算。同时,在计算过程中,CVflow能够并行加载网络的后续部分,实现了计算与数据加载的并行化,进一步提升了整体性能。

· 稳健的性能表现:由于大大减少了对DRAM的访问次数,并且实现了计算与数据加载的并行处理,CVflow架构在面临其他芯片模块(如CPU、GPU、ISP)同时高负载运行的场景时,仍能保持稳定的性能表现,从而确保了在各种复杂环境下的可靠性。

图3 AI模型的DAG切割示意图

· 硬件实现的算子

与GPU通过简单地堆砌计算单元来提升算力的方式不同,CVflow架构致力于通过实现高效的硬件算子来加速计算过程。CV3的CVflow架构,基于对深度学习网络的前瞻性研究,实现了超过100种常用算子的硬件化。这种设计策略使得CVflow在晶体管数量更少的情况下实现了出色的算力。

以8x8的矩阵乘法为例,传统的计算方式需要512个乘加(MAC)操作,但在CVflow架构中,其特有的矩阵乘法算子能够在单个计算指令周期内完成。此外,CVflow还支持多种融合算子的应用。例如,对于常见的2D/3D卷积与池化操作,CVflow的转换工具能够自动将这两个操作融合为一个硬件算子操作,从而有效减少了数据吞吐量和计算周期,进一步提升了整体性能。

· 非结构化的稀疏加速

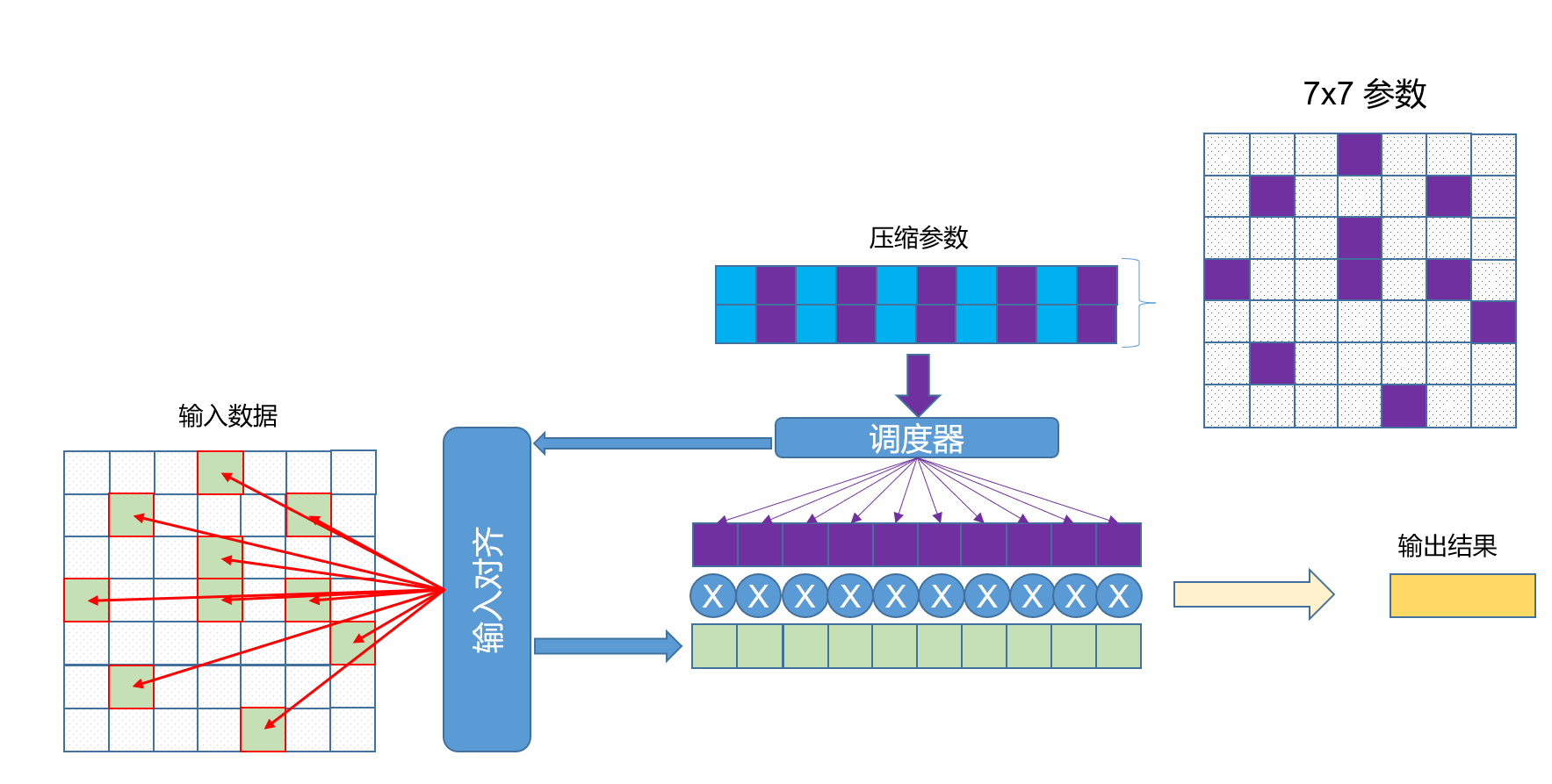

通过将AI模型稀疏化,去除冗余参数, CVflow架构带来了显著的性能提升,具体而言:

· CVflow工具能够自动压缩网络参数,这减少了芯片端加载AI模型所需的时间。

· 芯片端的CVflow硬件调度器具备智能分析能力,可以自动识别并跳过不必要的计算,从而显著降低了计算量。

· 无需对AI模型结构进行调整, 从而实现了算法的一次性开发和无缝部署。这种特性简化了模型部署过程,使得模型开发人员无需担心模型结构的兼容性问题,可以专注于算法的优化和创新。

· CVflow工具链提供了多种稀疏策略来保证AI模型稀疏后的精度。

以7x7卷积为例,未进行稀疏化之前,每次卷积操作都需要用到全部的49个参数,并且会执行49次乘加(MAC)操作。然而,当实施了80%的稀疏化后,情况发生了显著变化:参数量减少了60%,这意味着存储和传输的效率大大提升;计算量减少了80%,从而极大地提高了卷积操作的效率。这种CVflow独有的稀疏化技术对于优化AI模型的性能和资源消耗至关重要。

图4 CVflow网络稀疏化示例

· 支持多种量化格式

CV3的CVflow架构具有强大的数据格式支持能力,可以支持 4, 8, 16, 32的定点数据格式和16, 32位的浮点数据格式。CVflow工具能够针对每一层网络参数和输入输出数据进行精确的动态范围分析,从而确定最优的量化精度,实现高效的混合精度部署。这一特性使得CV3在处理不同数据类型和规模的任务时,能够灵活适应并发挥最佳性能。

2024年国际消费电子展(CES)期间,安霸展出了基于CV3平台的自动驾驶研发车辆,并为受邀客户提供试驾体验。此次展出进一步验证了CV3 CVflow架构芯片的强大实力,即便面对自动驾驶场景的大算力、高带宽的复杂计算需求,也能游刃有余地应对。

2023年,特斯拉实现了首个端到端大模型自动驾驶系统,将原本庞大的30万行的人工规则算法精简至仅2000行代码。随着驾驶数据的不断积累,自动驾驶技术正朝着端到端大模型的方向发展。 面对未来大模型自动驾驶时代的算力与内存墙挑战,专为自动驾驶设计的CV3-AD系列芯片凭借第三代CVflow架构,以芯片架构创新的方式,突破大算力芯片的内存墙的限制,为大模型算法提供了强大的硬件支持,助力高级辅助驾驶以及自动驾驶技术的普及与发展。

文章投诉热线:182 3641 3660 投诉邮箱:7983347 16@qq.com