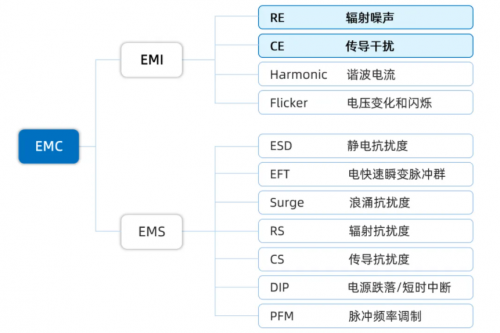

EMC即Electromagnetic Compatibility,是电磁兼容性的简称,指设备或系统在其电磁环境中符合要求运行,并不对其环境中的任何设备产生无法忍受的电磁骚扰的能力。EMC (电磁兼容性) 又分为EMI (电磁干扰)和EMS (电磁敏感度) 两部分内容。要弄清楚EMC设计,首先我们要了解几个概念,以下图为例:

(图源:英诺赛科公众号)

其中,RE和CE由于不确定性大、变量多等因素,导致其难度更大、耗时更长而受到大家的普遍关注。CE又可分为差模噪声(Differential mode Noise,简称DM)与共模噪声(Common mode Noise,简称CM)。

本文档将基于英诺赛科65W超小电源(采用InnoGaN器件)的测试,给出氮化镓电源RE和CE的基本原理,并分享了一些实用的调试方法和指导。

差模噪声DM

源头:功率电路周期开关电流经过BUS电容滤波后,少量残余电流经线路传输到输入口和LISN。

路径:沿着L、N线以幅值相同、方向相反的方式传播。

(反激QR电路,差模噪声的传输示意图,图源:英诺赛科公众号)

主要影响频段:≤5MHz

下图即为原始噪声和差模噪声的曲线(差模噪声波形是电源在无差模滤波的情况下,采用共模噪声滤波措施消除共模噪声后的CE波形);其中差模噪声随频率升高逐步衰减,在5MHz时,噪声幅值已可以满足6db裕量要求。

(差模噪声示意图,图源:英诺赛科公众号)

差模噪声滤除方法

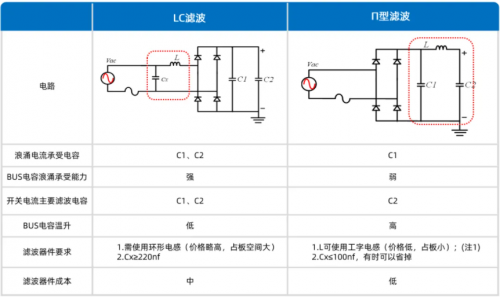

差模噪声滤除方法有LC滤波和π型滤波,下面为两种滤波方式的对比:

(图源:英诺赛科公众号)

注:LC滤波结构,差模电感 L 在交流线路上,电压和电流波动大,如采用磁路不闭合的工字电感,电流波动产生的交变磁力线对周围器件的影响大;而π型滤波电路,差模电感 L 在两个BUS电容中间,电压和电流波动均较小,故此处采用工字电感对周围影响小。

共模噪声CM

源头:GaN管D极的高频开关电压波形

传播路径:

1)通过Cps、Cse流向副边和大地(主)

2)通过Cpe直接流向大地(次)

3)其中,Cpe « Cps, Cpe « Cse

反激QR电路,共模噪声流动路径示意图,图源:英诺赛科公众号

将共模噪声流动路径提取出来,并对其进行简化后得到如下示意图:

共模噪声电路等效示意图,图源:英诺赛科公众号

其中Cpe电容相比Cps和Cse要小很多,故流过Cpe路径的共模噪声也要少得多,下面的分析均忽略流过Cpe的共模噪声。

下图为原始噪声及共模噪声(增加差模滤波措施后的噪声)的波形:

(图源:英诺赛科公众号)

故CE噪声范围内共模噪声的影响频段为150KHz~30MHz。

共模噪声滤波措施

措施一:Y电容

功率电路的原副边之间增加Y电容,为共模噪声提供了低阻抗的内部回流路径。

措施二:变压器绕组屏蔽技术

在变压器内增加屏蔽绕组是反激电源(包括CCM,QR、ACF、aZVS、AHB)等拓扑电路消除共模噪声问题常用的方法。增加变压器屏蔽绕组,其作用是在变压器内部增加一个与原噪声电压相位相反的噪声,该噪声对原共模噪声进行消减。

措施三:镍锌电感

共模噪声中的高频段噪声(≥10MHz噪声)

源头:电源内(寄生)电感、电容谐振产生的噪声峰值;

路径:与中、低频段CM噪声相同;

抑制方法:采用小感量锰锌或镍锌电感。

磁场干扰

噪声机理:磁场干扰源产生的交变磁力线耦合到输入滤波器件上,在输入滤波器件的线圈内产生的感应噪声,该感应噪声大多越过滤波电路,直接进入L、N线和LISN。

磁场干扰的源头包括(且不限于):

1.暴露在磁芯外的交变大电流导线(a、b、c);

2. 磁芯接合处(d);

(不同噪声源示意图,图源:英诺赛科公众号)

磁场干扰的特点有:

1)离干扰源越近,磁力线越密,受到的干扰越大;

2)暴露在磁芯外的交变大电流导线越长,干扰的区域越大;

3)线路中交变电流di/dt越大,产生的磁力线越强,产生的干扰也越强。

针对磁场干扰特点,其解决措施包括(且不限于):

1)减少交变大电流导线暴露在磁芯外的长度;

2)加大EMI滤波器件与噪声源的间距;

3)更换磁芯型号,利用变压器磁芯整体面进行屏蔽;

4)更换EMI滤波器件的摆放方向。

RE噪声

RE噪声测试基础RE,Radioactive Emission,即辐射噪声,是指通过空间电磁波传播的噪声。

电源内的开关原器件快速turn on/off时,其电压和电流波形的大dv/dt和di/dt包含的高频成分是RE噪声的主要源头。

RE测试相比CE测试,不确定性更大,如输入、输出线路长度,电源、负载的摆放方法等,都可能对RE结果产生影响。

在进行RE测试需注意下面事项:

1)待测电源(EUT)在测试台上居中放置,电源与负载间间距约为10cm;

2)输出充电线自然下垂,最低点与地板的间距40cm,超出的长度需用胶带包扎;

3)无其它上电设备,如输出端诱骗器等;如果必须存在,需做好屏蔽措施。

4)输入、输出线和插座等,用胶带固定住,避免移动;

5)板上输入、输出线路间不能有交叉;

6)保持测试桌面干净,不应放置其它样机或带金属的物品。

快充电源的RE噪声发射路径包括:

1)AC输入线路

2)电源本体

3)输出线路

这里以AC输入线为例,说明判定噪声发射线路的方法:

在输入线路上靠近电源口部增加磁扣,如果对应频点噪声有一定的降低(如降低5db以上),则可以认为输入线是该噪声的发射路径;噪声降低幅度越大,则其与输入线路发射的关联性越大。

如要判定电源本体噪声发射,可以在板上增加连接副边(或原边)的屏蔽金属,观察RE噪声的变化。

RE噪声消除方法

措施一:从源头消除

增加驱动措施,调整GaN器件的驱动电阻,可以降低GaN器件的开通速度,减小dv/dt和di/dt,降低噪声幅值。

措施二:从路径上入手

1)增加镍芯电感:增加镍锌电感(或小感量的锰锌),可以增加高频噪声进入输入、输出线路的阻抗,减少噪声经线路的发射;

2)增加屏蔽措施:增加屏蔽金属可以降低电源本体的噪声发射;

3)增加Y电容:Y电容为高频噪声提供低阻抗回路路径,减少噪声进入输入、输出线路。

关于英诺赛科:由骆薇薇博士创立,英诺赛科专注于第三代半导体氮化镓的应用与研发,是全球首家实现量产8英寸硅基氮化镓晶圆的公司,同时也是全球最大的8英寸硅基氮化镓器件制造商,也是全球唯一具备产业规模提供全电压谱系的硅基氮化镓半导体产品的公司。

免责声明:市场有风险,选择需谨慎!此文仅供参考,不作买卖依据。

文章投诉热线:157 3889 8464 投诉邮箱:7983347 16@qq.com